随着嵌入式系统复杂性的不断提高,软件缺陷的数量也在显著地增加。即使工程师是天才,零缺陷仍是一种幻想。尽管如此,对这种理想目标的追求应该是任何严肃的项目管理的终极目标。 除了良好的系统架构和彻底的技术实施之外:(a)尽可能完整的测试;(b)应对现场错误的预防措施是及时以最好的产品质量开发出产品的重要前提。

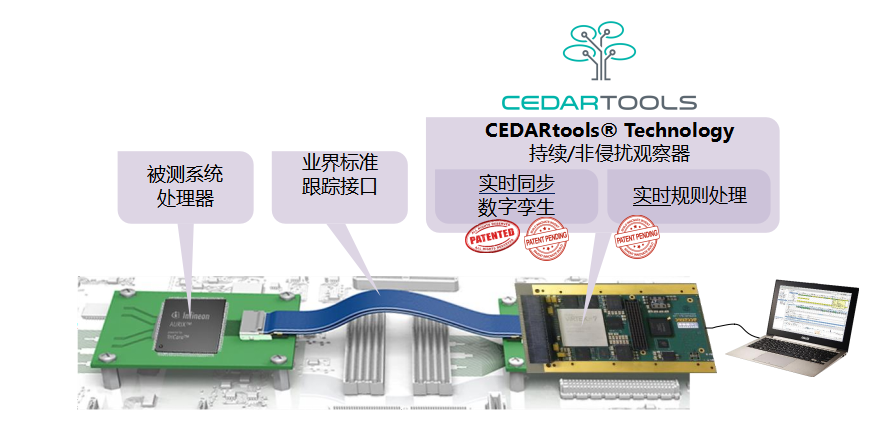

完善的测试和有效的调试的关键因素是可观察性--而且不对系统产生侵扰。CEDARtools利用复杂的电子设备和智能软件,创建受监控处理器的数字孪生表现形式,以执行实时覆盖率测量和运行时性能检查。

CEDARtools 是业界首个针对嵌入式系统不插装、持续实时观察的工具,对已经发布的代码进行监测且并不插装,在高级别功能测试时不插装,测量复杂的时间性能而不干扰系统的运行。

图1 CEDARtools实时跟踪数据采集分析模块

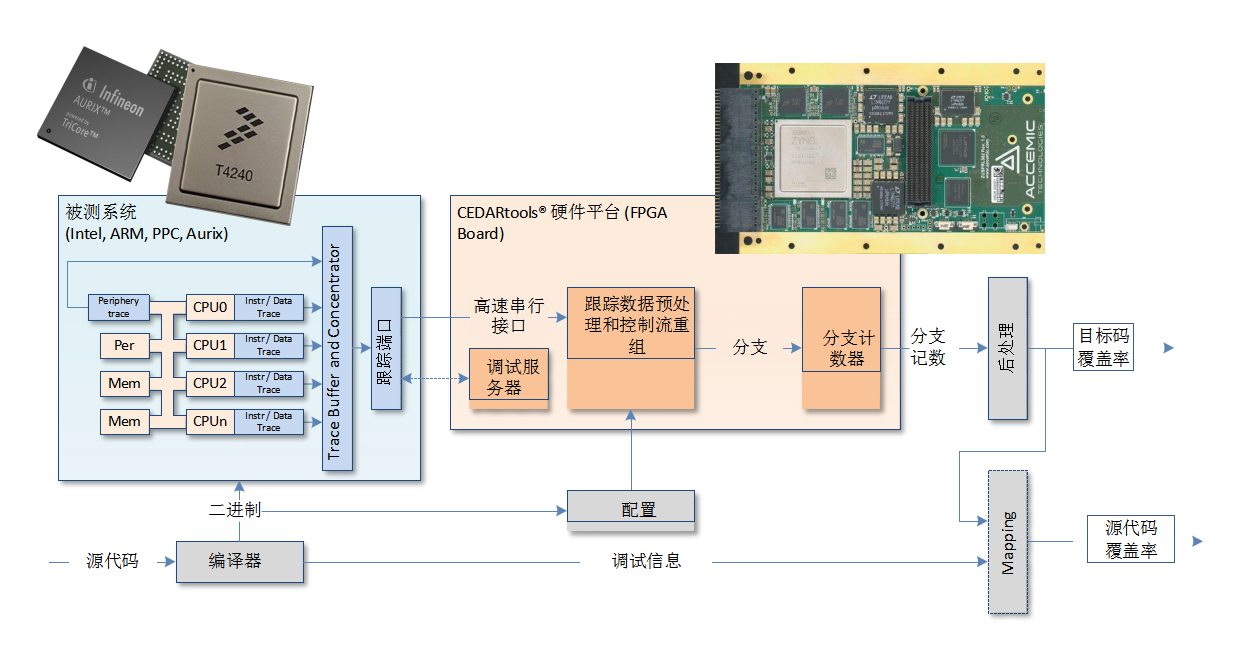

CEDARtools充分利用了现代处理器中集成的跟踪和调试单元(例如Arm®Coresight™、英特尔® Processor Trace、英飞凌MCDS),例如英飞凌AURIX™、恩智浦QorIQ®、英特尔Atom®和Arm®Cortex®这些处理器。它们的跟踪单元将CPU及其外围设备的运行细节展现给外部。但是,在运行时每秒会产生几GBit的跟踪数据,这些数据通过传统的并行跟踪端口或更现代,更可靠的串行接口(Nexus Aurora,Arm®HSSTP,Infineon AGBT,PCIe)输出。

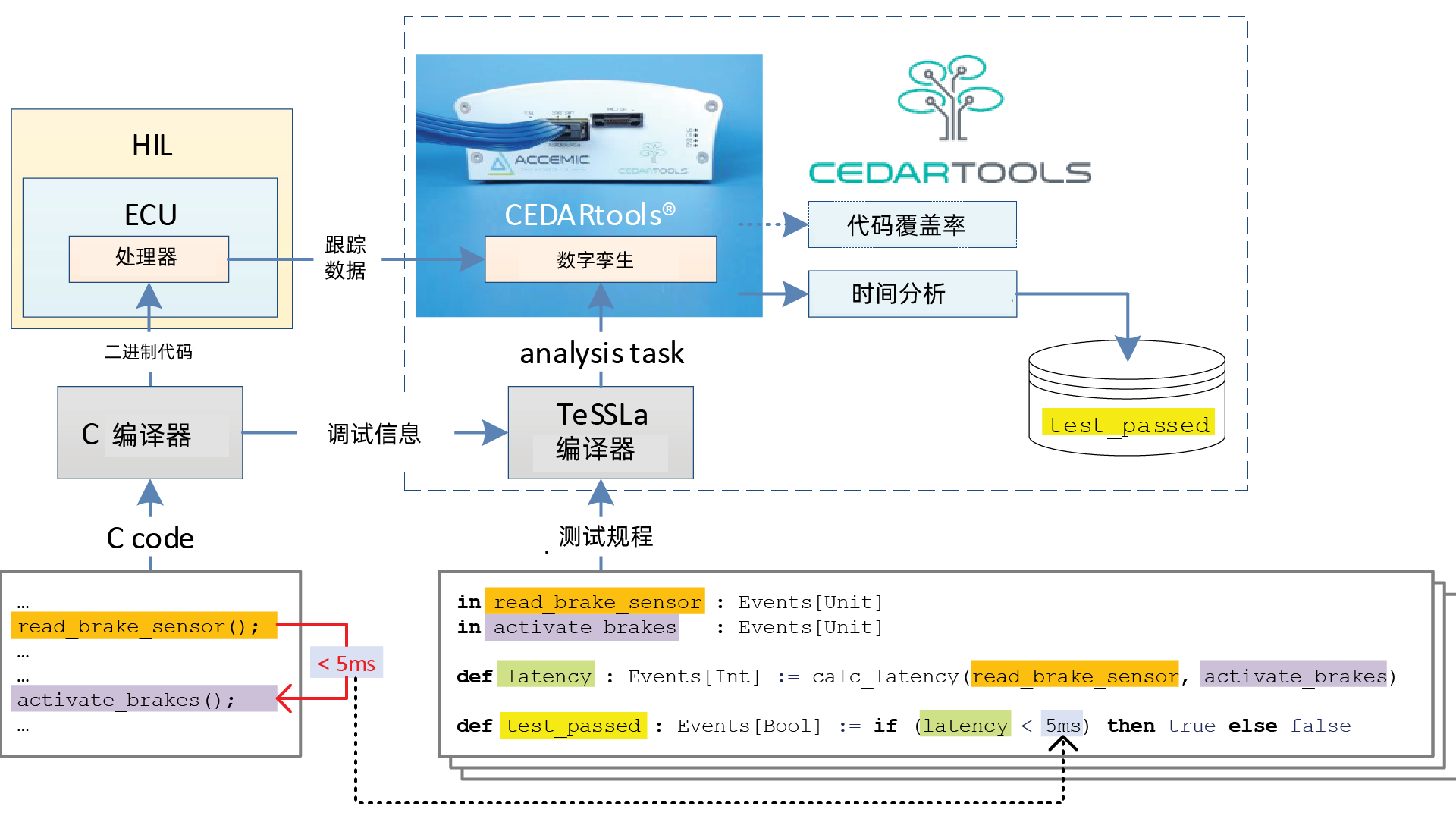

图2 CEDARtools系统示意图

支持所有级别的测试,执行目标码级别的结构化覆盖率分析(分支和语句覆盖率,性能测量),同时可以反向标注到源代码。

在任意时间片段,采用TeSSLa高级语言可以指定多种时间约束条件。软件运行所产生的追踪数据的存储和离线处理耗时是以前很棘手的问题,CEDARtools利用先进的硬件技术和智能软件可以轻松处理大多数标准处理器所产生的几个G的追踪数据流,例如如下处理器:

● Arm® Cortex®-A (通过HSSTP, PCIe 和 parallel4)

● Infineon Aurix™ TC2xx, TC3xx (通过 AGBT)

● NXP QorIQ® P- and T-series (通过 Aurora 和 PCIe)

● Intel® Atom® E39x0 (通过 PCIe 和 USB4)

主要特性

● 实时、在线、持续地对嵌入式处理器进行观测

● 在较高时间占用的复杂条件上触发

● 支持多核

● 多个观察焦点

● 自动化操作

● 支持语句覆盖率

● 支持分支覆盖率

● 性能测量(执行过的指令统计)

● 在目标码级别上进行测量

● 在发布(release)代码上实时测量分析

● 不插装代码

● 没有缓冲区大小的限制

产品价值

● 测试工具库中需求强烈的工具

● 强大的工具,可以发现捕获难以发现的缺陷

产品应用

● 直接测试发布的产品代码,不需要插装代码,在目标码级别上开展结构化测试

● 在发布代码上开展性能测量

● 复杂的时序验证,通过TeSSLa高级语言进行配置

● 对影响的链路进行测量

在被测系统运行时对跟踪数据进行实时分析相比跟踪数据的脱机分析是根本性飞跃,因为它有效消除了中间缓冲需求带来的瓶颈。但是,有两个主要技术挑战需要克服:

1.必须对高度压缩的跟踪数据流进行解压缩,并且必须重建CPU的控制流。这种苛刻的计算通常必须处理1 GHz以上的时钟频率运行的多个快速CPU的执行跟踪数据。该解码可能会受到不同操作系统(例如Linux、RTMS或FreeRTOS)引入的其他抽象和间接调用的进一步挑战。

2.必须将重构的控制流映射为对应的事件,以便开展各种后续分析任务。例如,(a)记录用于分支覆盖的信息,或者(b)可以根据时间逻辑规范来计算和验证性能属性。

图3 CEDARtools运行概览

图3的ADAS(高级驾驶辅助系统)例子演示了自动化、非侵扰、持续监视时间的约束条件,持续检查在读取刹车传感器read_brake_sensor() 和激活刹车 activate_brakes()之间的时间间隔少于5毫秒,发布的产品二进制文件(不需软件插装)加载到处理器中。在集成测试或者硬件在环系统测试(或者现场观察)过程中,处理器产生的追踪数据流通过并行端口或者串行高速接口(Nexus Aurora, Arm® HSSTP, Infineon AGBT, PCIe)输出。这个过程将基于FPGA的数字孪生表示与对应的被测系统的进程相同步。当执行预定义的指令read_brake_sensor()和activate_brakes()时,将产生事件,然后可以针对指定的时间属性即时检查事件。使用的事件处理单元可以通过TeSSLa语言进行编程,并且可以并行监视大量时间属性。TeSSLa对宏的支持可以适配各种行业标准,例如AUTOSAR TIMEX或AMALTHEA。

CEDARtools解决方案利用事件处理单元本地执行低级TeSSLa运算符。因此,它们仅针对给定的监视任务进行了重新编程。不需要专用的FPGA逻辑综合。因此,可以在几秒钟内将高级属性描述的更改应用于跟踪数据流。另外,CEDARtools硬件也可以配置为测量结构覆盖率(语句覆盖率,分支覆盖率,MC / DC)。

图4 覆盖率分析流程

图5 覆盖率统计结果

图6 CEDARtool采用的技术与传统技术的对比