SynaptiCAD是一款EDA(电子设计自动化)工具集合,包括HDL输入、仿真、测试、波形分析、管脚映射工具等等,分为四大类多个独立的工具模块。

1. Timing Diagram Editing

▷ Timing Diagrammer Pro

▷ WaveFormer Pro

▷ DataSheet Pro

2. VHDL & Verilog 仿真调试

▷ VeriLogger Extreme

▷ BugHunter Pro

▷ GigawaveViewer Pro

3. VHDL & Verilog Test Bench 生成

▷ WaveFormer Pro

▷ Reactive TB

▷ TestBencher Pro

4. VHDL 和 Verilog 代码转换

▷ V2V

Timing Diagram Editing

Timing Diagram Editing有三个功能工具,用户可根据预算与功能需求选择:

▷ Timing Diagrammer Pro

▷ WaveFormer Pro

▷ DataSheet Pro

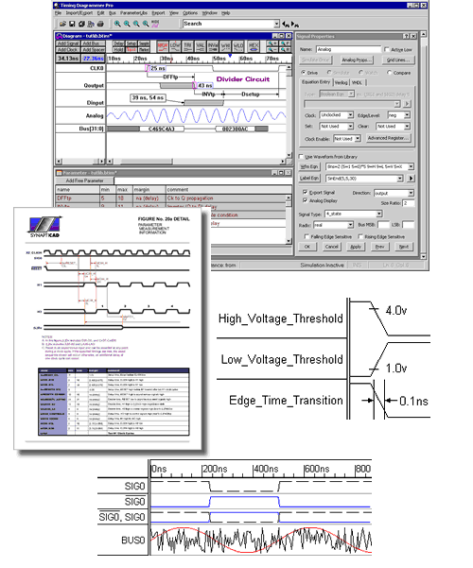

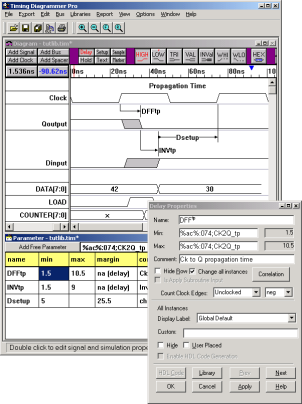

Timing Diagram Pro

Timing Diagrammer Pro 是入门级的时序图编辑器。

▷ 17年来持续发展

▷ 无调绘图环境

▷ 模拟/数字波形

▷ 高级时序分析

▷ 支持工业标准的TDML语言和零件库库

Timing Diagram Creation

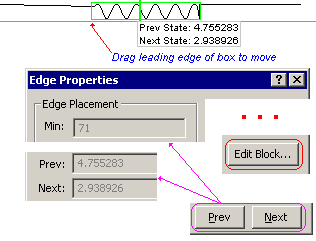

▷ 真正做到的最小/最大时序分析与延迟,设置和保持,也支持公式。

▷ 支持模拟信号的显示和生成。

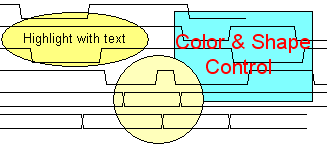

▷ 支持文本块注释和高亮显示

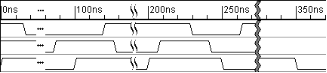

▷ 通过压缩标记隐藏了图中的时序片段

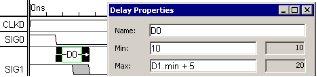

Timing Diagram Analysis

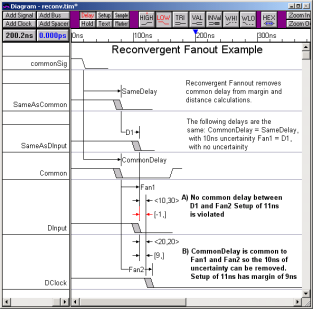

▷ 延迟、设置和保持参数

▷ 所有时序参数支持最小、最大以及公式设置

▷ 重新处理扇出时序计算

▷ 延迟相关延迟

▷ 准确建立时钟抖动和斜率模型

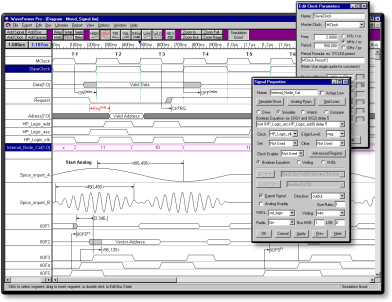

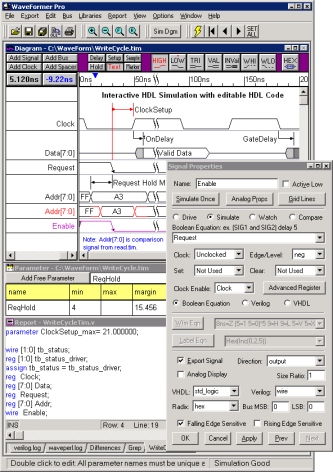

WaveFormer Pro

具有Timing Diagrammer Pro的所有功能, WaveFormer Pro 还增加了如下功能:

▷ 支持信号仿真,使得设计时序图更快、更准确

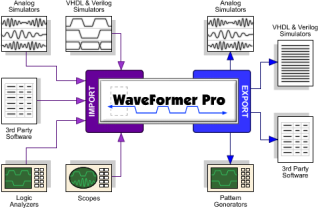

▷ 支持多种格式导入导出,包括VHDL、 Verilog、 SPICE、逻辑分析器和图形生成器。

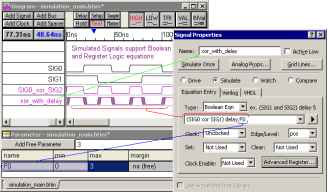

Timing Diagram Simulation

▷ 采用布尔量和已注册的逻辑公式可快速构建FPGA模型和胶合逻辑

▷ 支持多位寄存器和锁存器

▷ 生成用于导入外部模拟器VHDL或Verilog模型的时序图

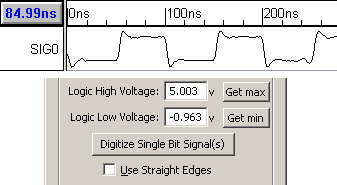

支持最小和最大时间的方程式: (SIG0 and SIG1) 门限时间延迟

(使用标准的VHDL/Verilog模拟器很难完成)

Waveform File Translation

WaveFormer支持超过43种格式,包括一个开放的Perl界面,以供用进行脚本开发。

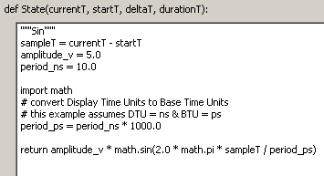

Analog Waveform Blocks

支持使用简单的基于python的方程式来创建可编辑的模拟波形块。

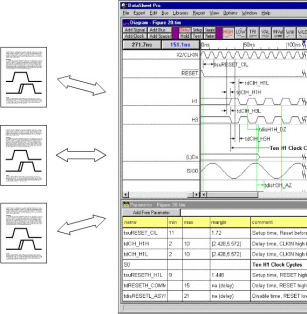

Datasheet Pro

DataSheet Pro是支持时序的最高级别,为设计人员和文档专业人员提供了一种标准化的方式来共同创建IC数据表。

▷ 工程管理

▷ 样式表

▷ 多个打印视图

▷ 支持从任何SynaptiCAD产品或其他TDML编辑器导入时序图

▷ 支持查看多个时序图

DataSheet Pro - OLE Editing

双击文字处理程序中嵌入的时序图,自动地调用正确的时序图文件打开DataSheet Pro。

DataSheet Pro–交互模式

▷ 将交互式数据表交付给客户。时序图可以位于行为Verilog模型之上,并在客户更改图表上的指令时重新进行模拟

▷ 支持在时序图上添加公司logo

▷ 直接在时序图上添加说明

VHDL & Verilog 仿真调试工具

SynaptiCAD为Verilog 和VHDL调试提供一系列的工具:

▷ VeriLogger Extreme:快速编译Verilog模拟器;

▷ BugHunter Pro:支持VHDL和Verilog模拟器的图形调试;

▷ Gates-on-the-Fly :Verilog网表编辑;

▷ GigaWave Viewer:从仿真器测试设备上查看波形;

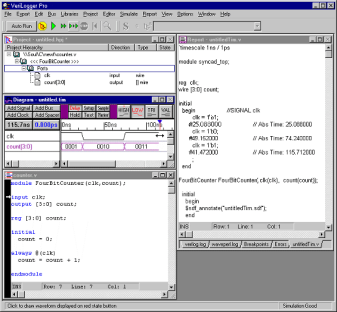

VeriLogger Extreme

VeriLogger Extreme 是一个高性能编译代码Verilog2005的仿真器,同时具备一些System Verilog支持,显著减少了仿真调试时间。

▷ 支持基于SDF时序信息的RTL和门级仿真的快速仿真。

▷ 支持所有主要ASIC和FPGA供应商的设计库和设计流, 包括 MicroSemi/Actel、Altera、LSI Logic、QuickLogic 和 Xilinx。

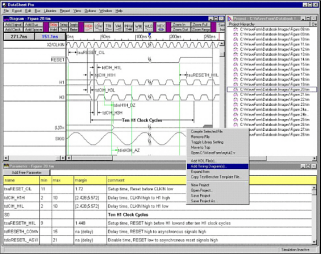

BugHunter Pro

BugHunter Pro 是一个用于VHDL、Verilog和SystemC 仿真器的图形化调试环境。

支持所有主要仿真器

▷ 支持波形观察

▷ 项目模型的分层显示

▷ 具有颜色语法编辑功能的编辑器

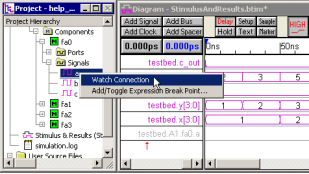

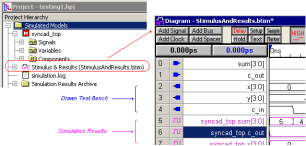

BugHunter – 单元级测试

可使用单元级的测试功能快速测试小模块。 BugHunter 为 Stimulus and Results 图中信号生成激励代码,并把该代码作为项目的输入。

Stimulus and Results 图表还可以显示模拟过程中的所有监视信号。

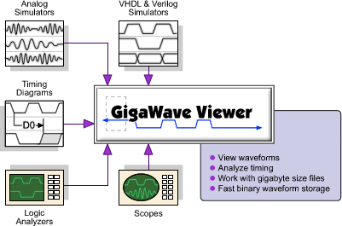

GigaWave查看器

GigaWave查看器结合SynaptiCAD的波形查看器和高性能波形压缩引擎来处理multi-gigabyte文件。

▷ 生成压缩的二进制文件,以便快速查看

▷ 查看VCD文件

▷ 查看逻辑分析器文件

▷ 运行批处理模式

VHDL/Verilog Test Bench Generation

SynaptiCAD有三个级别的图形化Test Bench Generation,以满足测试需求的类型和复杂性。

▷ WaveFormer Pro – 单图Test Bench Generation

▷ Reactive TB – 对被测模型有反应的单图

▷ TestBencher Pro – 多图Test Bench Generation

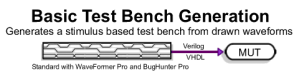

VHDL/Verilog Test Bench Generation

WaveFormer Pro、 Data Sheet Pro和BugHunter 具备基本的激励Test Bench Generation生成功能。

▷ 绘制的波形用于生成激励模型

▷ BugHunter特性紧密集成到仿真环境中,实现对设计模型的快速交互测试

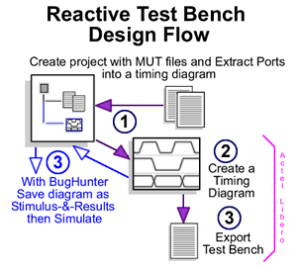

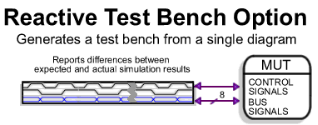

Reactive Test Bench Option

从单个时序图中创建自测试测试Test Bench Generation,用于在仿真测试中形成错误报告和对模型做出的反应。

▷ 这个选项还允许生成“clocked test benches”,该Test Bench Generation基于一个或多个时钟信号更新激励

▷ 反应性Test Bench Generation生成选项可以添加到 WaveFormer Pro, DataSheet Pro和BugHunter Pro中

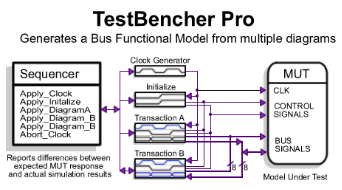

TestBencher Pro

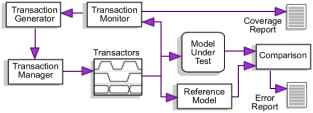

最高级别的Test Bench Generation是通过 TestBencher Pro生成,TestBencher

Pro允许用户设计总线功能模型,使用多个时序图来定义事务器,并使用序列处理程序来应用图表事务。testbenchPro可以与BugHunter一起购买或作为一个独立的工具购买。

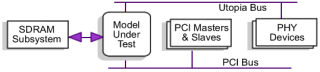

TestBencher Pro-基于规范的验证

问题: 验证与不同协议交互的SOC模型。

解决办法: 使用testbench生成架构,然后自动生成事务处理程序、事务数据和验证结果的逻辑。

TestBencher Pro 生成VHDL and Verilog代码

▷ Timing Diagrams 定义可重复使用的定时事务

▷ 顶级模板定义事务序列并监视MUT状态

▷ 生成受约束的随机数据结构

▷ 仿真器和编译器的外部控制

▷ 可以扩展到支持其他语言

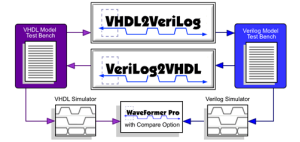

VHDL Verilog Translation

▷ VHDL2Verilog和Verilog2VHDL是命令行工具,用于自动翻译HDL源代码

▷ BugHunterPro作为图形化环境用户用作执行和测试翻译

▷ SynaptiCAD还提供了完整的翻译服务