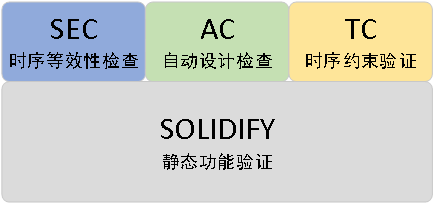

Solidify是一套全面的高效验证工具,旨在帮助设计人员验证FPGA研发过程中的复杂设计。Solidify工具包包含Solidify(静态功能验证)、SolidSEC(时序等效性检查)、SolidAC(自动设计检查)和SolidTC(时序约束验证)。

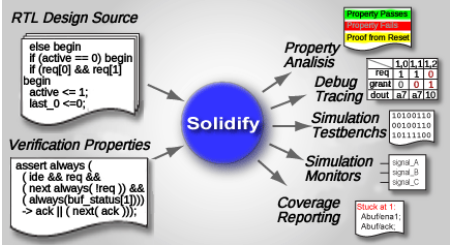

Solidify-静态功能验证

作为高性能静态功能验证器,Solidify工具可提供完整的属性验证环境并具有强大的属性验证功能,包括但不限于多语言支持、源代码调试、接口仿真等高级功能。在多年的迭代更新中,已广泛应用于多个不同的行业中。

功能

● 属性验证,多个形式化引擎,时序冗余去除,无TestBench环境代码漏洞检测,源代码调试

● 可定制引擎,属性代码覆盖,复位时序预测

● 分层验证、多时钟支持、内存模型生成、多线程、验证数据库、属性连接、传递属性跟踪等

支持的代码语言

● Verilog,VHDL,SystemVerilog,mixed

● SVA,PSL,OVA,OVL,HPL property languages

● VCD,SDC,LIB

输出

● 特性分析,调试跟踪,波形

● Testbench代码生成,可综合监视器生成,属性语言交叉翻译

● 覆盖率报告

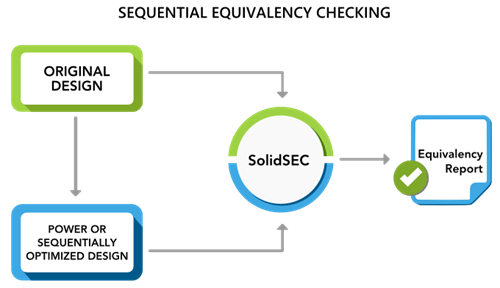

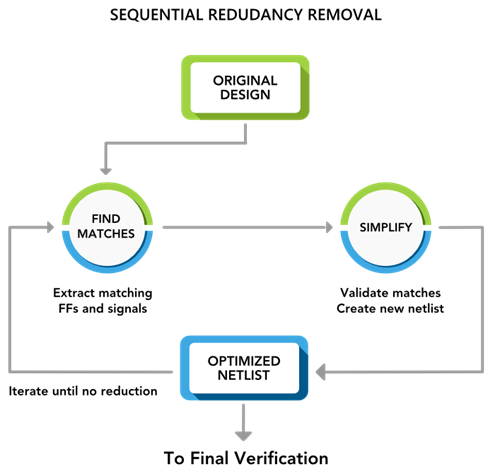

SolidSEC-时序等效性检查

SolidSEC是一个,建立在Averant的形式验证技术之上强大的时序等效检查器。工具内包含支持RTL和门级设计的组合等效检查器(CEC)。经过多年与工业和教育领域的研究和合作开发,该工具可以集成到降功耗流程以及其他顺序优化中,为此类设计带来形式验证的力量。随着越来越复杂的低功耗设计技术,SolidSEC工具是保证整体设计正确性不可或缺的一步。

当前设计往往包含冗余管理逻辑,SolidSEC可通过简单的命令无缝集成到Solidify中来消除冗余设计并提高验证性能。强大的顺序冗余删除是任何现代和完整的属性验证工具所必需的。

功能

● 可处理百万级的门设计

● 支持Verilog、VHDL和混合语言

● 穷举分析

● 错误跟踪

● 可兼容标准低功耗流程设计

● 可支持第三方调试工具的集成

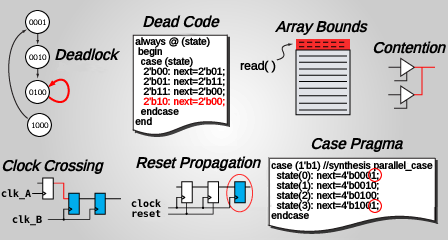

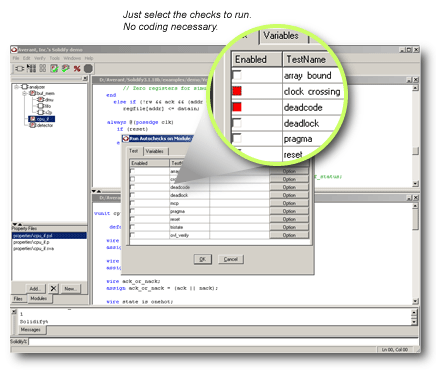

SolidAC-自动设计检查

SolidAC会自动检查设计中是否存在许多常见但难以发现的问题,用户只需要选择要运行的检查即可对自动读取的RTL源进行检查。

功能

● 死代码

● 死锁/活锁

● 跨时钟域(CDC)

● CDC与数据稳定性和格雷码检查

● Full / parallel case pragma

● 复位传播

● 争用

● 数组越界

● x值传播

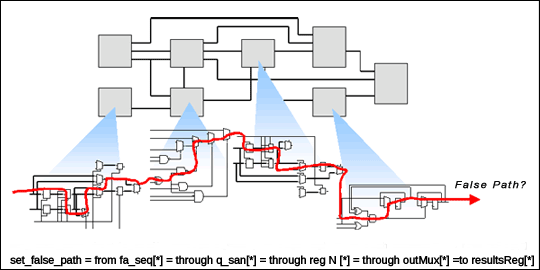

SolidTC-时序约束验证

时序约束是逻辑设计中三个最关键的问题之一。调试不正确的时序约束会使项目的调试工作徒劳无功。SolidTC是一种基于形式化验证技术的时序约束验证工具,可快速、详尽地验证虚假路径和多周期路径(MCP)约束。SolidTC支持Verilog、VHDL和混合设计语言。它以SDC文件作为输入,并为每个约束输出通过/失败。SolidTC与所有当前设计流程无缝集成。

SolidTC工具也是一种时序约束验证器,该工具基于Solidify引擎可用于检查SDC文件中声明的错误路径和多周期路径的有效性,能快速、详尽的验证和查找异常的时序。这些时序异常的正确性。

功能

● 处理数百万级门设计

● 支持Verilog、VHDL和混合语言

● 分析全面

● 运行时工作级的能力控制

● 错误跟踪生成

● 仅需要设计和SDC文件

● 对当前设计流程没有影响